Intel showed off advances that could keep Moore’s Law on track.

Image Credit: Intel

Did you miss a session from GamesBeat Summit Next 2022? All sessions are now available for viewing in our on-demand library. Click here to start watching.

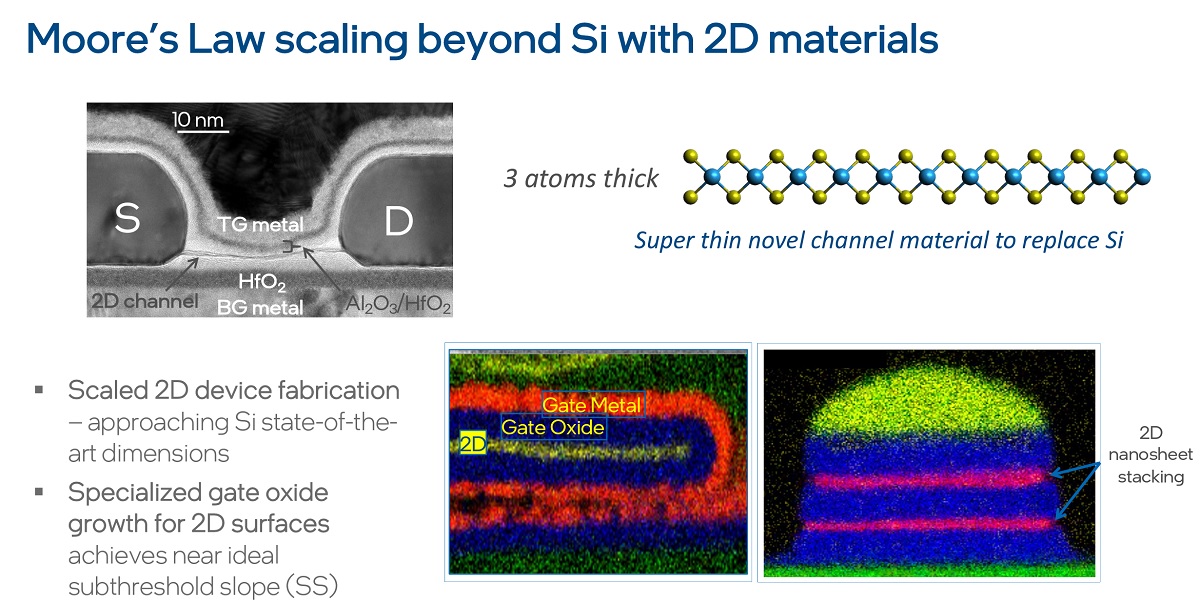

Intel announced that its researchers foresee a way to make chips 10 times more dense through packaging improvements and a layer of a material that is just three atoms thick. And that could pave the way to putting a trillion transistors on a chip package by 2030.

Moore’s Law is supposed to be dead. Chips aren’t supposed to get much better, at least not through traditional manufacturing advances. That’s a dismal notion on the 75th anniversary of the invention of the transistor. Back in 1965, Intel chairman emeritus Gordon Moore predicted the number of components, or transistors, on a chip would double every couple of years.

That law held up for decades. Chips got faster and more efficient. Chip makers shrank the dimensions of chips, and goodness resulted. The electrons in a miniaturized chip had shorter distances to travel. So the chip got faster. And the shorter distances meant the chip used less material, making it cheaper. And so Moore’s Law’s steady march meant that chips could get faster, cheaper, and even more power efficient at the same time.

But Moore’s Law really depended on brilliant human engineers coming up with better chip designs and continuous manufacturing miniaturization. During recent years, it got harder to make those advances. The chip design ran into the laws of physics. With atomic layers a few atoms thick, it wasn’t possible to shrink anymore. And so Nvidia CEO Jensen Huang recently said, “Moore’s Law is dead.”

Event

Intelligent Security Summit

Learn the critical role of AI & ML in cybersecurity and industry specific case studies on December 8. Register for your free pass today.

Register Now

That’s not good timing, since we’re just about to start building the metaverse. Moore’s Law is vital to addressing the world’s insatiable computing needs as surging data consumption and the drive toward increased artificial intelligence (AI) brings about the greatest acceleration in demand ever.

A week after Nvidia’s CEO said that, Intel CEO Pat Gelsinger said that Moore’s Law is alive and well. That’s no surprise since he has bet tens of billions of dollars on new chip manufacturing plants in the U.S. Still, his researchers are backing him up at the International Electron Devices Meeting. Intel made it clear that these advances are may five to ten years out.

In papers at the research event, Intel described breakthroughs for keeping Moore’s Law on track to a trillion transistors on a package in the next decade. At IEDM, Intel researchers are showcasing advances in 3D packaging technology with a new 10 times improvement in density, said Paul Fischer, director and senior principal engineer in components research at Intel, said in a press briefing.

“Our mission is to keep our options for process technology rich and full,” he said.

These packages have been used in innovative ways lately; Intel rival Advanced Micro Devices announced that its latest graphics chip has a processor chip and six memory chips — all connected together in a single package. Intel said it collaborates with government entities, universities, industry researchers, and chip equipment companies. Intel shares the fruits of the research at places like the IEDM event.

Intel also unveiled novel materials for 2D transistor scaling beyond RibbonFET, including super-thin materials just three atoms thick. It also described new possibilities in energy efficiency and memory for higher-performing computing; and advancements for quantum computing.

“Seventy-five years since the invention of the transistor, innovation driving Moore’s Law continues to address the world’s exponentially increasing demand for computing,” said Gary Patton, Intel vice president of components research and design enablement, in a statement. “At IEDM 2022, Intel is showcasing both the forward-thinking and concrete research advancements needed to break through current and future barriers, deliver to this insatiable demand, and keep Moore’s Law alive and well for years to come.”

The transistor’s 75th birthday

Commemorating the 75th anniversary of the transistor, Ann Kelleher, Intel executive vice president and general manager of technology development, will lead a plenary session at IEDM. Kelleher will outline the paths forward for continued industry innovation – rallying the ecosystem around a systems-based strategy to address the world’s increasing demand for computing and more effectively innovate to advance at a Moore’s Law pace.

The session, “Celebrating 75 Years of the Transistor! A Look at the Evolution of Moore’s Law Innovation,” takes place at 9:45 a.m. PST on December 5.

To make advances required, Intel has a multi-pronged approach of “growing signficance and certainly a growing influence within Intel” to look across multiple disciplines.

Intel has to move forward in chip materials, chip-making equipment, design, and packaging, Fischer said.

“3D packaging technology is enabling the seamless integration of chiplets,” or multiple chips in a package, he said. “We’re blurring the line between where silicon ends and packaging begins.”

Continuous innovation is the cornerstone of Moore’s Law. Many of the key innovation milestones for continued power, performance and cost improvements over the past two decades – including strained silicon, Hi-K metal gate and FinFET – in personal computers, graphics processors and data centers started with Intel’s Components Research Group.

Further research, including RibbonFET gate-all-around (GAA) transistors, PowerVia back side power delivery technology and packaging breakthroughs like EMIB and Foveros Direct, are on the roadmap today.

At IEDM 2022, Intel’s Components Research Group said it is developing new 3D hybrid bonding packaging technology to enable seamless integration of chiplets; super-thin, 2D materials to fit more

transistors onto a single chip; and new possibilities in energy efficiency and memory for higher-performing computing.

How Intel will do it

Researchers have identified new materials and processes that blur the line between packaging and silicon. Intel said it foresees moving from tens of billions of transistors on a chip today to a trillion transistors on a package, which can have a lot of chips on it.

One way to make the advances is through packaging that can achieve an additional 10 times interconnect density, leading to quasi-monolithic chips. Intel’s materials innovations have also identified practical design choices that can meet the requirements of transistor scaling using a novel material just three atoms thick, enabling the company to continue scaling beyond RibbonFET.

Intel’s latest hybrid bonding research presented at IEDM 2022 shows an additional 10 times improvement in density for power and performance over Intel’s IEDM 2021 research presentation.

Continued hybrid bonding scaling to a three-nanometer pitch achieves similar interconnect densities and bandwidths as those found on monolithic system-on-chip connections. A nanometer is a billionth of a meter.

Intel said it is looking to super-thin ‘2D’ materials to fit more transistors onto a single chip. Intel demonstrated a gate-all-around stacked nanosheet structure using a thin 2D channel just three atoms thick, while achieving near-ideal switching of transistors on a double-gate structure at room temperature with low leakage current.

These are two key breakthroughs needed for stacking GAA transistors and moving beyond the fundamental limits of silicon.

Researchers also revealed the first comprehensive analysis of electrical contact topologies to 2D materials that could further pave the way for high-performing and scalable transistor channels.

To use chip area more effectively, Intel redefines scaling by developing memory that can be placed vertically above transistors. In an industry first, Intel demonstrates stacked ferroelectric capacitors that match the performance of conventional ferroelectric trench capacitors and can be used to build FeRAM on a logic die.

An industry-first device-level model captures mixed phases and defects for improved ferroelectric hafnia devices, marking significant progress for Intel in supporting industry tools to develop novel memories and ferroelectric transistors.

Bringing the world one step closer to transitioning beyond 5G and solving the challenges of power efficiency, Intel is building a viable path to 300 millimeter GaN-on-silicon wafers. Intel breakthroughs in this area demonstrate a 20 times gain over industry standard GaN and sets an industry record figure-of-merit for high performance power delivery.

Intel is making breakthroughs on super-energy-efficient technologies, specifically transistors that don’t forget, retaining data even when the power is off. Already, Intel researchers have broken two of three barriers keeping the technology from being fully viable and operational at room temperature.

Intel continues to introduce new concepts in physics with breakthroughs in delivering better qubits for quantum computing. Intel researchers work to find better ways to store quantum information by gathering a better understanding of various interface defects that could act as environmental disturbances affecting quantum data.

GamesBeat’s creed when covering the game industry is “where passion meets business.” What does this mean? We want to tell you how the news matters to you — not just as a decision-maker at a game studio, but also as a fan of games. Whether you read our articles, listen to our podcasts, or watch our videos, GamesBeat will help you learn about the industry and enjoy engaging with it. Discover our Briefings.